SSDAC 基板の電源を入れるとうまく立ち上がらないことがあります。エージングをして(暖めてから?)電源を入れると立ち上がるので動かすときはエージングをしていました。オリジナルとレイアウトが異なるのでそのためと思ってしばらくはそのままにしていましたが、やっぱり気持ちが悪いので原因を探りました。

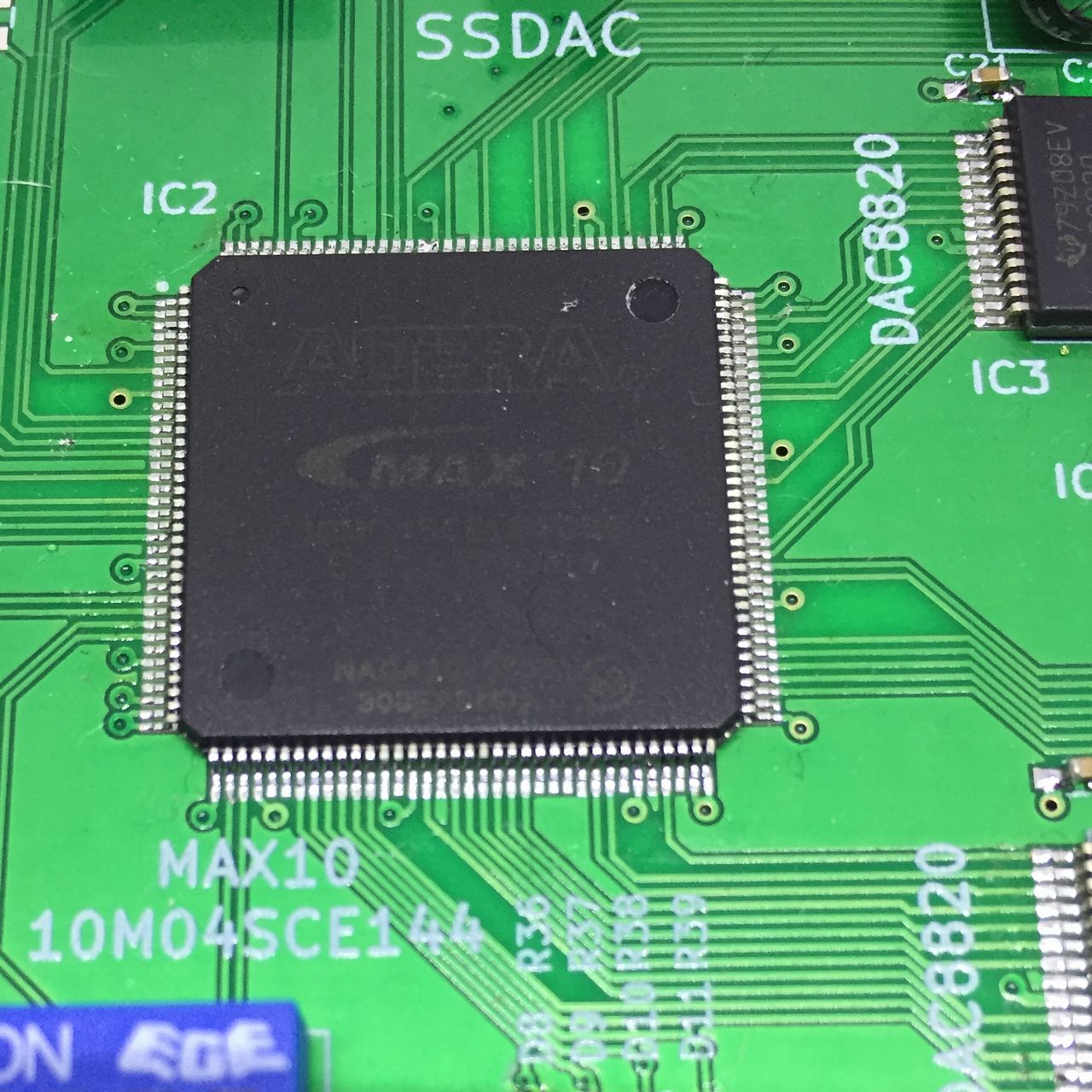

オリジナルの回路と違う電源周りなどをいろいろ探りましたが特に改善は見られません。FPGA を触ると正常に動き出すのでFPGA(10M04SCE144)周りがおかしいのではとオリジナルの回路と比較しましたが違っているところは見つかりません。

そこでインテルの資料を確認することにしました。MAX10 FPGA コンフィギュレーションユーザーガイドでは 3.2.1 JTAG コンフィギュレーションのセットアップの項目でnSTATUS,CONFIG_DONE,nCONFIGは10kΩでプルアップされています。SSDAC の回路図ではプルアップされていません。特にnCONFIGは入力端子(CMOS)なのでオープン状態にしておくのは良くありません。FPGAはその昔、FLEX10Kというのを使ったことがありますが、それ以来全く使っておらずもっぱらCPLDで設計していたのでそもそもnCONFIGという存在も忘れていました。😂

これらの信号をリワークするにしても0.5mmピッチのFPGAの足にはんだ付けしてプルアップ抵抗を付けるなんて芸当はとてもできません。でも、運よくnCONFIGピンの隣が電源ピンになっています。隣のピンとショートさせるのはなんとかできます。

他の信号は電源に直接接続することはできないし、プルアップも無理なのでとりあえずこれで電源をいれてみます。

本来はnSTATUS,CONFIG_DONE,nCONFIGはプルアップしなければいけませんがこのままで動かしていくことにします。再度基板を作るような時には直しますが今のところその予定はないのでこのままです。

気になるのはオリジナルの方はどうなっているのだろうとググってみると同じような対策をしていました。そりゃそうですね😄。FPGAのプログラムも更新があるようです。

さて、音ですが当初は少しおとなしく感じたのですがエージングのせいか聴き込んでいるとだいぶ力強くなりました。演奏者が近くにいるようで繊細なニュアンス(音)も聞き取れるようです。これはBBG + ArchBoticです。USB->Combo384経由だとそれに薄いベールがかかったような印象ですがそれでもなかなかのもです。一聴の価値はあります。

と、オリジナルのSSDACキットですが販売ページにいくと販売終了となっていました。予約申し込み書のページはまだあるので、当初の限定販売は終了して再度予約受付しているということなのでしょうか。