ChatGPTに、

「10進カウンターの回路とテストベンチをVHDLで書いて。」

とお願いしたところ以下のようなVHDLコードを書いてくれました。

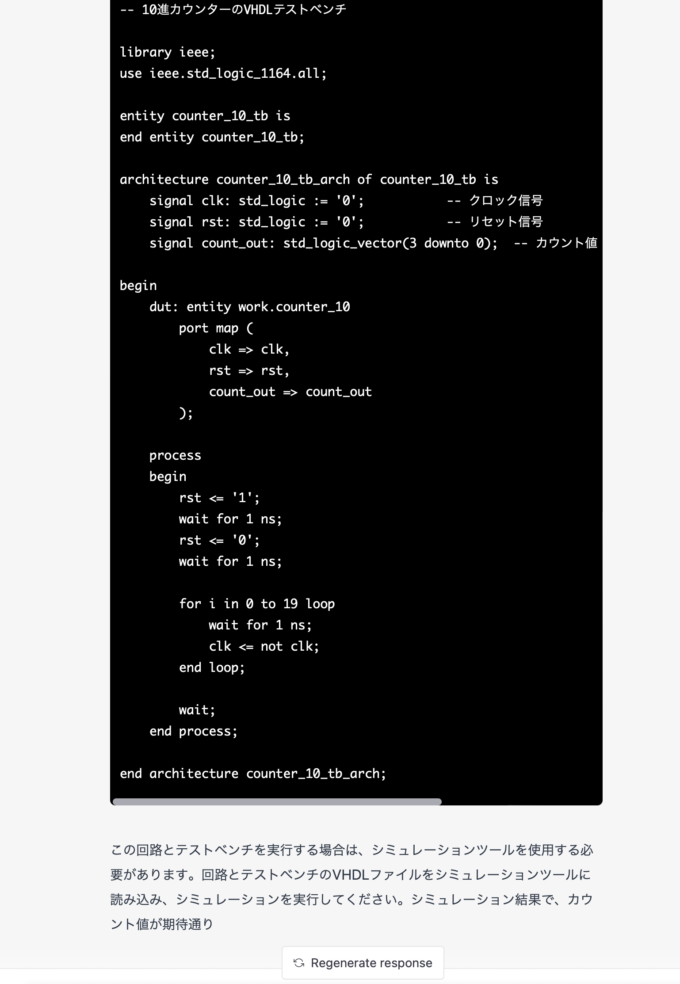

そして、VHDLテストベンチです。

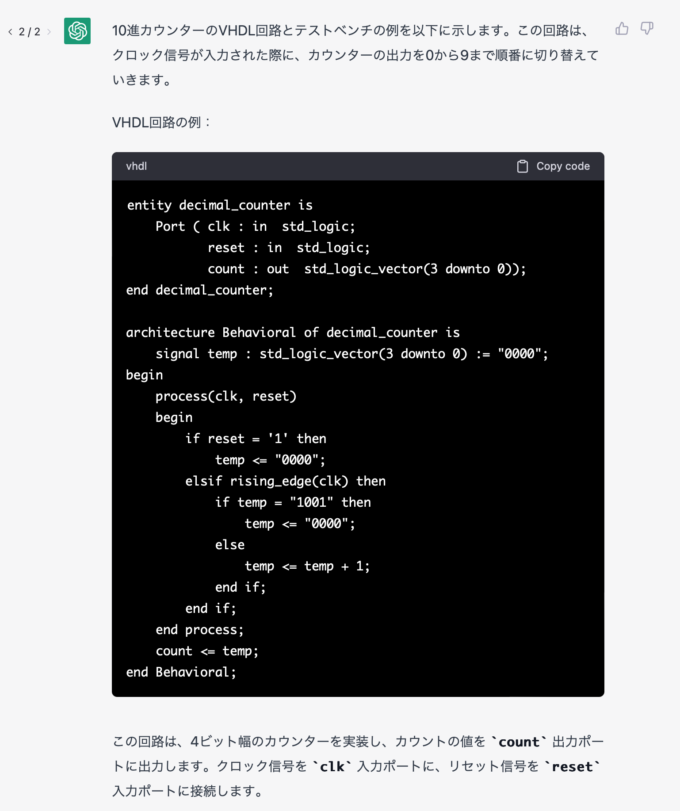

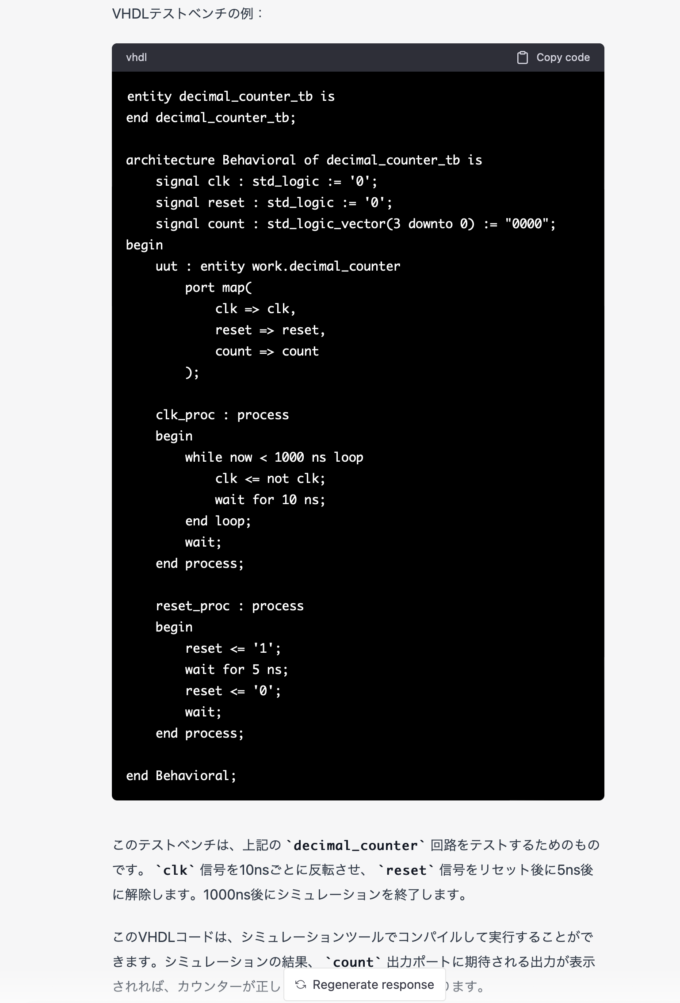

説明文の最後が尻切れトンボだったので、もう一度同じ文言でお願いした(Regenerate response)ところ、今度は別のVHDLコード例を書いてくれました。

ほとんど同じ時間にお願いしたので(同じコードが出てくると思っていて)別のコードが出てきたので驚きました。

さて、ChatGPTが初めに書いてくれたVHDLコードをそのままコピペして、Quartus Primeでコンパイルしたところ以下のように「”to_unsigned”が使われているけど、宣言されていない」と怒られます。

Error (10482): VHDL error at counter_10.vhd(33): object "to_unsigned" is used but not declared

最終行の一つ前の行の

std_logic_vector(to_unsigned(count, 4))

は、integer型の count 変数を4ビットのstd_logic_vector型に変換するためのコードです。to_unsigned 関数は、引数として渡された数値をunsigned型に変換します。unsigned型は、ビット幅を指定することで任意のビット数で表現できます。この場合、count 変数をunsigned型に変換して、ビット幅を4ビットに設定しています。そして、unsigned型の値を std_logic_vector型に変換するために、std_logic_vector 型のコンストラクタに渡しています。

ここで使われている”to_unsigned”関数を有効にするにはnumeric_stdライブラリを宣言する必要があるということです。なので

use ieee.numeric_std.all;

を追加します。これでQuartus Primeのコンパイルがとおり、期待したシミュレーション結果が得られました。

そして、次のVHDLのコードですが、これは明らかに記述が足りていません。VHDL回路及びVHDLテストベンチともライブラリパッケージの宣言がありません。

必要なライブラリパッケージの宣言を追加することで、Quartus Primeでのコンパイル・シミュレーションができています。

ChatGPTで簡単な回路のVHDL記述を試しました。今回の例ではライブラリパッケージの宣言漏れはありましたが、基本的な回路記述、テストベンチの記述は修正せずに使えました。もう少し複雑な回路でも試してみようと思いますが、これは便利?ですね。